เทคโนโลยีบัสคอมพิวเตอร์ (Computer Bus Technology) 1/3

อัปเดท : 20 มิถุนายน พ.ศ.2546 , แสดง : 36,922 , ความคิดเห็น : 3

ระบบบัสของระบบคอมพิวเตอร์ได้รับการออกแบบให้ทำงานในรูปแบบของการแข่งขันเพื่อแย่งใช้ทรัพยากร นั่นคือในเวลาหนึ่งๆ สามารถมีการแย่ง เพื่อขอใช้บัสได้จากอุปกรณ์หลายๆ ตัว แต่ทว่าจะมีเพียงอุปกรณ์หนึ่งตัวเท่านั้นที่สามารถใช้งานได้ ประสิทธิภาพการใช้งาน bandwidth ของบัสสำหรับโพรเซสเซอร์ แต่ละตัวจะเป็นค่าผกผันกับจำนวน โพรเซสเซอร์ ที่ที่แย่งเรียกใช้ bus ด้วยเหตุนี้ เครื่องคอมพิวเตอร์ที่ผลิตเชิงธุรกิจที่มีรูปแบบเป็น bus-based-multi-processor ส่วนมากมักถูกออกแบบให้มีจำนวนโพรเซสเซอร์ไม่มาก ด้วยความเรียบง่ายและการลงทุนที่ไม่สูงในการผลิต ส่งผลให้ได้เครื่อง multi-processor ที่มีขนาดเล็ก คือมีจำนวน โพรเซสเซอร์อยู่ประมาณ 4 – 16 ตัวตามศักยภาพเทคโนโลยีในปัจจุบัน

Backplabe bus Specification

Backplane bus จะทำการเชื่อมต่อโพรเซสเซอร์ (processor), แหล่งเก็บข้อมูล (data storage) และอุปกรณ์เชื่อมต่อต่างๆ (peripheral device) ในลักษณะแบบ tightly couple (คือการเชื่อมต่อที่ใช้ common-bus เพื่อการสื่อสารระหว่างอุปกรณ์ เช่นโพรเซสเซอร์หลายตัวเรียกใช้ memory จากแหล่งเดียวกัน ตรงกันข้ามกับ loosely couple ซึ่งโพรเซสเซอร์แต่ละตัวมี memory ของตัวเอง) การออกแบบการทำงานของบัสจะต้องออกแบบให้อุปกรณ์ต่างๆที่อยู่บนบัสสามารถสื่อสารกันได้โดยที่ไม่รบกวนการทำงานของอุปกรณ์อื่นๆที่เรียกใช้บัสนั้นอยู่ เนื่องจากการที่มี โพรเซสเซอร์มากกว่าหนึ่งตัว ดังนั้นจึงต้องมีการกำหนดกฎเกณฑ์เพื่อให้สามารถรองรับการเรียกใช้จากโพรเซสเซอร์หลายตัว โดยการตัดสินว่าโพรเซสเซอร์ ใดสามารถใช้งานบัสได้นั้น จะต้องมีการกำหนดข้อตกลงเรื่องเวลา (Timing protocol) และเพื่อให้แน่ใจว่าการส่งข้อมูลเป็นไปตามลำดับจึงต้องมีการกำหนดกฎการปฏบิติงาน (Operational rule)ไว้ด้วย

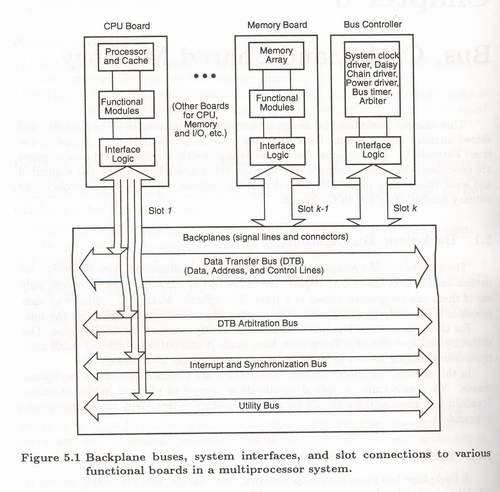

สายสัญญาณบนระบบ backplane bus จะถูกรวมเป็นกลุ่มบัสหลายๆ กลุ่ม แยกตามฟังก์ชันการทำงาน ดังแสดงในภาพ 5.1 กลุ่มสายสัญญาณทั้ง 4 ที่แสดงนั้นจะคล้ายคลึงกับระบบบัส 64-bit

แผงการทำงานต่างๆ (board) จะถูกต่อเข้ากับส่วนรับอุปกรณ์(slot)บนบัส แต่ละส่วนรับอุปกรณ์จะมีช่องสำหรับเสียบแผงการทำงานอยู่หนึ่งช่องหรืออาจมากกว่านั้น ดังแสดงในรูป 5.1 ตัวอย่างเช่น ส่วนรับอุปกรณ์บนระบบ VME backplane จะมีส่วนรับอุปกรณ์ที่มีช่องเสียบแบบ 96 ขาอยู่หนึ่งหรือสองช่อง

1 Data Transfer Bus (DTB)

Bus แบบนี้จะทำหน้าที่ในการรับส่งข้อมูล(data) , ตำแหน่งข้อมูล (Address) และสัญญาณควบคุม (control line) สำหรับส่วน addressing line จะทำหน้าที่ในการกระจายตำแหน่งข้อมูล และตำแหน่งอุปกรณ์ไปยังอุปกรณ์ตัวอื่นๆ จำนวนของ address line จะแปรผันแบบลอกการิทึมกับจำนวน address เช่นหากมี 1024 address จำนวนสายสัญญาณที่ใช้จะเป็น log 2 1024 = 10 สาย) ส่วนสายแปลงค่าaddress (address modifier line) จะถูกใช้ในกรณีที่ต้องการกำหนด address แบบพิเศษ และจำนวนสายข้อมูล (data line)จะแปรผันตามความยาว memory word คือ หากระบบเป็นแบบ n- bit-word ดังนั้นจำนวนสายข้อมูลเป็น c*n (เมื่อ c เป็นค่าคงที่ใดๆ )

ตัวอย่างเช่น ระบบ VME ที่ได้รับการปรับปรุงใหม่ให้มี 32 address line และ 32 data line แต่สาย address สามารถถูกสลับใช้เป็นสาย data ได้ในช่วงรับส่งข้อมูล ดังนั้นจากระบบนี้อาจเรียกได้ว่ามี 32 address line และ 64 data line สำหรับสายควบคุมสัญญาณ (Control line) จะถูกใช้สำหรับเพื่อตรวจจับว่าการทำงานเป็นการอ่าน (read) หรือเป็นการเขียน (write), ตรวจจับเวลา (timing control), and และตรวจจับเงื่อนไขความผิดพลาด (error condition)

2 Bus Arbitration and Control

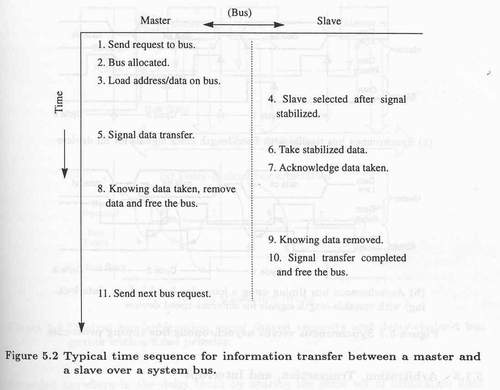

กระบวนการที่จะกำหนดว่าจะยก DTB ให้กับผู้เรียกใช้ตัวใดเรียกว่ากระบวนการ arbritation ในช่วงของการทำงานของกระบวนการนี้ จะมีสายสัญญาณจำนวนหนึ่งถูกจับจองไว้ใช้งานเพื่อการนี้ โพรเซสเซอร์ที่เป็นผู้เรียกขอใช้บัส (ตัวที่จะส่งสัญญาณ) เรียกว่า master ส่วนโพรเซสเซอร์ (หรืออุปกรณ์อื่น) ที่เป็นตัวรับสัญญาณเรียกว่า slave

สายสัญญาณ Interrupt เป็นสายสัญญาณที่ใช้จัดการงาน interrupt ซึ่งมักเป็นงานที่ได้รับจัดอันดับความสำคัญไว้ สายสัญญาณชุดหนึ่งที่ถูกจับจองไว้แต่แรกทำหน้าที่จัดจังหวะ (synchronize) งานที่เกิดขึ้นระหว่างโพรเซสเซอร์ หลายตัวที่ทำงานพร้อมกัน

สายสัญญาณ Utility ทำหน้าที่ส่งสัญญาณที่ไม่เกี่ยวเนื่องกับข้อมูลแต่จำเป็นสำหรับระบบ เช่นสัญญาณนาฬิกา (Clocking), สัญญาณการเปิดระบบ และสัญญาณการปิดระบบ

ดังนั้นเห็นได้ว่า Backplane bus ประกอบด้วยส่วนสายสัญญาณ (signal line) และช่องเสียบอุปกรณ์ (connector) โดยที่จะมีแผงการควบคุมพิเศษตัวหนึ่ง (controller board) ที่ใช้เก็บลอจิกการควบคุมต่างๆ เช่น ระบบสัญญาณนาฬิกา, ตัวจัดการกระบวนการ arbitration หรือเรียกว่า arbiter, ตัวควบคุมเวลา และตัวควบคุมพลังงาน

3 Functional Modules

Functional module เป็นกลุ่มวงจรอิเลกทรอนิกที่อยู่บนแผงการทำงานที่จะทำหน้าที่ในการทำงานใดงานหนึ่งโดยเฉพาะ ตัวอย่าง functional module เช่น

- Arbiter: ทำหน้าที่รับสัญญาณเรียกใช้จาก master และทำหน้าที่ส่งสัญญาณอนุญาตให้ใช้ (bus grant) กลับไปให้ผู้เรียกใช้นั้น โดยจะส่งไปให้เพียง 1 ผู้เรียกใช้เท่านั้น ณ เวลาหนึ่งๆ

- Bus timer: ทำหน้าที่จับเวลาการส่งข้อมูลบน DTB หากว่าใช้เวลานานเกินไป อุปกรณ์ตัวนี้จะทำหน้าที่หยุดการส่งข้อมูลบน DTB นั้น

- Interrupter : ทำหน้าที่สร้างสัญญาณ interrupt พร้อมกับรายละเอียด ID ของการ interrupt เพื่อส่งให้ interrupt handler

- Location motor : ทำหน้าที่ติดตามสถานะการรับส่งข้อมูลบน DTB

- Power monitor : ทำหน้าที่ติดตามสถานะของแหล่งพลังงานของระบบ และจะส่งสัญญาณออกไปเมื่อพบว่าแหล่งส่งสัญญาณไม่เสถียร( unstable)

- System clock driver : ทำหน้าที่สร้างสัญญาณนาฬิกาเพื่อส่งให้ utility bus นอกจากนั้นบนระบบบัสจะมี board interface logic ซึ่งทำหน้าที่ปรับระดับของแรงต้านทานในสายสัญญาณ (impedance) , propagation time, ค่ายุติการส่งข้อมูล (termination value) ระหว่างตัวบัสและแผงวงจรให้สอดคล้องกัน

Physical limitation

เนื่องด้วยข้อจำกัดทางด้านวิทยาการทางด้านไฟฟ้า(Electrical limitation), กลไกการทำงาน (mechanical limitation) และการประกอบ (packaging limitation) ส่งผลให้จำนวนแผงการทำงานที่เสียบต่อเข้ากับbackplane หนึ่งๆถูกจำกัดตามไปด้วย แต่ในขณะเดียวกัน backplane-bus หลายตัวสามารถต่อเชื่อมเข้ากับโครง backplane (backplane chassis) เดียวกันได้

ตัวอย่างเช่น โครงของบัสแบบ VME backplane สามารถมี backplane-busบนโครงเดียวกันได้1-3 ตัว โดยที่บัสสองตัวสามารถที่จะทำงานร่วมกันในลักษณะของการเป็น shared bus ของโพรเซสเซอร์ และหน่วยความจำหลายๆตัวได้ ส่วนบัสที่เหลืออีกหนึ่งตัวทำหน้าที่เป็น local-bus ที่เชื่อมต่อโพรเซสเซอร์ (local processor) ไปยังหน่วยความจำเสริม (additional memory) และแผง Input/Output (I/O board)

การจะขยายบัสนั้นสามารถทำได้ แต่มักจะทำได้ค่อนข้างยากเพราะต้องขึ้นอยู่กับข้อจำกัดทางด้านรูปแบบการประกอบ(Packaging) เสียมาก

Address and Timing Protocols

แผงวงจรที่เชื่อมต่อกับระบบบัสมีอยู่ 2 แบบ คือ active board และ passive board สำหรับแผงวงจรแบบ active เช่น โพรเซสเซอร์ สามารถทำงานได้ทั้งแบบ master และ slave ในช่วงเวลาที่ต่างกัน แต่แผงวงจรที่เป็นแบบ passive เช่น memory จะทำงานได้แต่รูปแบบ slave เท่านั้น

อย่างไรก็ตามในเวลาหนึ่งๆ จะมี Master เพียงหนึ่งตัวเท่านั้นที่เรียกใช้บัสได้ แต่ทว่า slave มากกว่าหนึ่งตัวสามารถที่จะตอบกลับ (respond) masterได้ในเวลาเดียวกัน

Bus Addressing

การทำงานของ Backplane-bus จะถูกขับเคลื่อนด้วยสัญญาณจังหวะนาฬิกาที่คงที่ที่เรียกว่า ‘bus cycle’ สำหรับค่าของ bus cycleนี้จะขึ้นอยู่กับลักษณะทางไฟฟ้า (electrical characteristic), กลไกการทำงาน (mechanical characteristic) และรูปแบบการประกอบ (packaging characteristic) ของ backplaneนั้น สัญญาณที่วิ่งอยู่บนเส้นสัญญาณของบัสจากจุดเริ่มต้นไปยังจุดปลายทางอาจประสพกับการล่าช้า (delay) ที่ไม่เท่ากัน

การออกแบบ backplane จะถูกจำกัดไว้ด้วยขนาดๆหนึ่งที่จะไม่ส่งผลให้เกิดการบั่นทอน(skew)ของข้อมูลที่ถูกส่งในช่วงสัญญาณเวลานั้น และเพื่อเป็นการเร่งความเร็วของการทำงาน ดังนั้นbus cycle ของบัสคนละชุดที่ทำงานด้วยกันอาจจะมีจังหวะการทำงานที่คาบเกี่ยวกัน(overlap) สำหรับสิ่งที่ส่งผลกระทบให้เกิดการล่าช้าในการทำงานได้แก่ ส่วนควบคุมการทำงานของตัวต้นทาง (source’s line driver) , ส่วนรับข้อมูลปลายทาง (destination’s receiver), ความจุของส่วนต่อเชื่อมอุปกรณ์ (slot capacitance) , ความยาวของสายสัญญาณ และ bus loading effect เช่นจำนวนแผงวงจรที่เชื่อมต่อ

Bus cycle ไม่ได้ถูกใช้ในการส่งข้อมูล (data transfer) เสียทั้งหมด เพื่อเป็นการปรับคุณภาพของการทำงาน ระบบบัสควรได้รับการออกแบบให้ลดเวลาในขั้นตอนของการจัดการ request (request handling), arbritation, การระบุตำแหน่ง (addressing) และการจัดการเกี่ยวกับ interruption เพื่อให้ bus cycle ใช้สำหรับงานการส่งข้อมูลให้มากที่สุด

แต่ละแผงการทำงานจะถูกระบุไว้ด้วยหมายเลข slot เมื่อใดก็ตามที่หมายเลข slot ตรงกับค่าของ high-order ของสายสัญญาณ address เมื่อนั้นแผงวงจรนั้นจะถูกกำหนดให้เป็น slave การกำหนด address แบบนี้เอื้อให้สามารถกำหนด address โดยการใช้ซอฟท์แวร์ควบคุมได้ อันส่งผลให้การทำงานเกิดความคล่องตัวขึ้น

Broadcall and Broadcast

โดยทั่วไป bus transaction หนึ่งๆจะเกี่ยวข้องกับ master 1 ตัว และ slave 1 ตัวเท่านั้น แต่มีการทำงานที่เรียกว่า Broadcall ซึ่งจะทำการการอ่านข้อมูลจาก slave หลายตัว โดยที่ slave เหล่านี้จะส่งวางข้อมูลลงบนสายสัญญาณของบัส ลอจิกAND, OR จะถูกเรียกใช้ทำงานกับข้อมูลที่ส่งมาจากบรรดาslaveที่เหล่านี้ การทำงานแบบ Broadcall ถูกใช้ในงานตรวจจับสัญญาณ interrupt จากหลายแหล่ง

การทำงานแบบ Broadcast เป็นการเขียนข้อมูลไปยัง slave หลายๆ ตัว การทำงานแบบนี้จะใช้ในการเขียนข้อมูลไปยังcacheที่เป็นแบบ multi-cache

Synchronous Timing

วิธีการจัดจังหวะแบบนี้ ทุกๆ bus transaction จะเริ่มทำงาน ณ ตำแหน่งขอบของสัญญาณนาฬิกา ดังแสดงในภาพที่ 5.3a สัญญาณนาฬิกานี้จะถูกส่งไปยัง master ทุกตัวและ slave ทุกตัว ระยะเวลาของ clock cycleขึ้นกับการทำงานของอุกรณ์ที่ทำงานช้าที่สุดที่ต่อเชื่อมกับบัสนั้น

เมื่อข้อมูลถูกนำไปวางที่ Data line ตัว master จะส่งสัญญาณ data-ready เพื่อบอกให้ slave รู้ว่าเริ่มส่งข้อมูล เมื่อ slaveได้รับข้อมูลแล้วจะส่งสัญญาณ data-a

การจัดจังหวะแบบ Synchronous เป็นไปแบบเรียบง่าย ไม่ต้องการวงจรการควบคุมที่ซับซ้อน ดังนั้นจึงเป็นการลดต้นทุนไปในตัว วิธีการนี้เหมาะสำหรับการต่อเชื่อมอุปกรณ์ที่มีความเร็วการทำงานที่เท่ากัน หากอุปกรณ์ทำงานด้วยความเร็วที่ต่างกัน อุปกรณ์ที่ทำงานช้ากว่าจะฉุดให้ระบบบัสทำงานช้าไปด้วย

2. Asynchronous Timing

วิธีการจัดจังหวะแบบนี้ใช้พื้นฐานของการ handshaking (interlocking) ดังแสดงในรูป 5.3b โดยที่ไม่จำเป็นต้องอาศัยจังหวะสัญญาณนาฬิกา การทำงานเริ่มด้วย master นำข้อมูลวางที่บัสแล้วส่งสัญญาณ data-ready โดยที่สัญญาณขาขึ้นของ data-ready(1) จะทำการเรียกสัญญาณขาขึ้นของ data-accept(2) เมื่อข้อมูลถูกส่งไปแล้ว สัญญาณขาลงของ data-ready(3) จะเรียกสัญญาณขาลงของ data-accept(4) อันเป็นว่าการส่งข้อมูลชุดนี้เสร็จแล้ว การส่งข้อมูลจะเป็นแบบ ‘4-edge handshaking ‘ ไปเรื่อยๆ จนกว่าการส่งข้อมูลทั้งหมดเสร็จสิ้น

วิธีการแบบนี้จะไม่ขึ้นกับสัญญาณนาฬิกา ดังนั้นการทำงานของระบบบัสจึงยืดหยุ่นได้โดยที่ไม่ต้องจำกัดอยู่ที่ความเร็วของอุปกรณ์ ดังนั้นอุปกรณ์ที่ความเร็วไม่เท่ากันสามารถทำงานบนระบบบัสเดียวกันได้โดยที่ไม่ทำให้ความเร็วของการทำงานของอุปกรณ์ตัวอื่นช้าลง

Arbitration , Transaction , and Interrupt

กระบวนการตัดสินว่า Master ใดสามารถใช้งานบัสได้เรียกว่า ‘arbitration’ ส่วนช่วงเวลาที่master สามารถใช้งานบัสได้เรียกว่า ‘master tenure’ กระบวนการ arbitration ถูกออกแบบให้อนุญาต master เพียงหนึ่งตัวใช้งานบัสได้ ณ เวลาหนึ่งเท่านั้น ส่วนการจะตัดสินว่าmasterไหนสามารถใช้งานบัสได้นั้นเป็นไปตามกฎเกณฑ์ของลำดับความสำคัญ กระบวนการ arbitration และการส่ง bus-transaction สามารถเกิดได้พร้อมกันๆ บนบัสนั้น โดยอาศัยวิธีการส่งสัญญาณบนสายสัญญาณแยกกัน เพื่อให้สามารถทำงานทั้งสองอย่างไปพร้อมๆกันได้

1.Central Arbitration

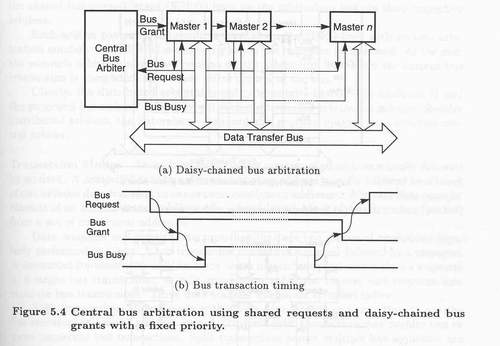

จากที่แสดงในรูป 5.4a วิธีการแบบ central arbitration จะใช้ arbiter กลางตัวหนึ่ง ส่วนmaster ต่างๆ จะมีการต่อเข้า arbiter ในรูปของการต่อแบบ daisy chain (เป็นการต่อยาวแบบลูกโซ่) จะมี master เพียงหนึ่งตัวที่ต่อตรงเข้ากับ arbiter นอกจากนั้นจะมีสายสัญญาณ ‘grant’ ที่จะส่งสัญญาณอนุญาตให้ใช้บัส แต่สายสัญญาณนี้จะต่อระหว่าง master หนึ่งไปยังอีก master หนึ่งไปเรื่อยๆ จนถึงตัวสุดท้ายMaster แต่ละตัวสามารถส่ง bus-request ได้ อย่างไรก็ตาม bus-request ทุกตัวจะร่วมใช้สายสัญญาณ bus-request เดียวกัน ซึ่งสัญญาณ bus-request นี้จะเรียกให้เกิดสัญญาณอนุญาตให้ใช้ (bus-grant) และสัญญาณ bus-grant นี่จะส่งให้เกิดสัญญาณ bus-busy

ด้วยวิธีการนี้ ลำดับความสำคัญของการใช้งาน(priority)จะถูกกำหนดตายตัวจากซ้ายไปขวา อุปกรณ์ที่ต่อเชื่อมทางด้านขวาจะได้รับอนุญาตให้ใช้บัสก็ต่อเมื่ออุปกรณ์ทางด้านซ้ายไม่ส่งสัญญาณ bus-request และเมื่อการส่ง transaction เสร็จสมบูรณ์แล้ว สัญญาณ bus-busy จะลดสัญญาณลง ส่งผลให้ bus-grant ลดสัญญาณลง และเปิดโอกาสให้สำหรับ bus-request ตัวต่อไป

ผลดีของวิธีการแบบนี้คือความเรียบง่ายของการทำงาน สามารถต่ออุปกรณ์อื่นๆเพิ่มได้ทันทีที่ปลายของ daisy chain แต่ข้อเสียคือ จะเป็นการกำหนดลำดับความสำคัญที่ตายตัวเกินไป และข้อเสียอีกข้อคือความล่าช้าของการส่งสัญญาณ bus-grant ไปยังอุปกรณ์ที่อยู่บน chain เพราะสัญญาณต้องวิ่งผ่าน master ตัวอื่นๆทางซ้ายมือก่อน และเมื่อใดก็ตามที่อุปกรณ์ตัวใดตัวหนึ่งไม่ทำงาน อุปกรณ์ที่เหลือทั้งหมดทางขวามือจะไม่สามารถใช้งานบัสได้ เนื่องจากสัญญาณ bus-grant ไม่สามารถถูกส่งผ่านไปยังอุปกรณ์ทางขวาได้

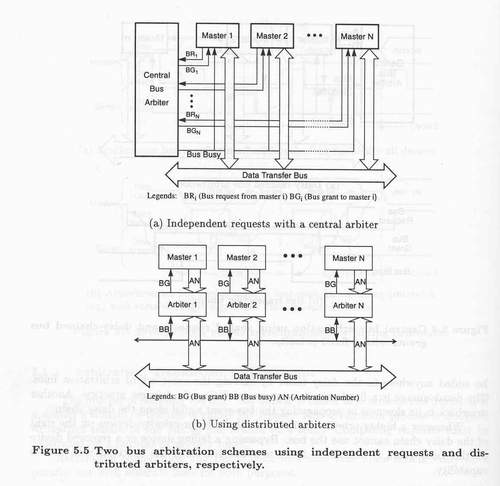

2.Independent Request and Grant

แทนที่จะใช้สายสัญญาณ Bus-request และ bus-grant ร่วมกันเหมือนดังวิธี Central Arbitration สำหรับวิธีการนี้ masterแต่ละตัวจะมีสายสัญญาณ local bus-request และ bus-grant ต่อตรงเข้า Central Arbiter และไม่มีการต่อแบบ daisy chain สำหรับวิธีการนี้การกำหนดว่าจะเลือกให้ Master ใดได้ใช้งานบัสนั้นจะเป็นไปตามหลัก priority-based สำหรับอุปกรณ์ I/O และเป็นไปตามหลัก fairness-based สำหรับอุปกรณ์ที่เป็นโพรเซสเซอร์ ในกรณีที่ โพรเซสเซอร์ ถูกออกแบบมาให้ใช้งานในลักษณะที่แตกต่างกันออกไป เช่น ใช้งานควบคุม front-end host, executive processor, back-end slave processor กรณีเหล่านี้สามารถใช้หลักpriority-basedได้

ข้อดีของวิธีการนี้คือความยืดหยุ่นในการทำงาน และความเร็วในการเลือกโพรเซสเซอร์ที่ดีกว่า เมื่อเทียบกับวิธีของ Daisy chain แต่ข้อเสียคือต้องมีจำนวนชุดเส้นสัญญาณสำหรับการทำ arbitration (request, grant) มากตามจำนวน โพรเซสเซอร์

3. Distributed Arbitration

แนวคิดการทำงานแบบ Distribute Arbitration แสดงไว้ดังรูปที่ 5.5b วิธีการนี้ master แต่ละตัวจะมี arbiter พร้อมกับหมายเลข arbitration หมายเลขนี้จะใช้สำหรับกระบวนการ arbitration เมื่อมีอุปกรณ์มากกว่าหนึ่งตัวต้องการใช้บัสmasterตัวที่สามารถใช้งานได้คือ master ที่หมายเลข arbitration ที่มีค่าสูงสุด

วิธีการเปรียบเทียบว่าหมายเลข arbitrationใดมีค่ามากที่สุดมีขั้นตอนดังนี้ คือ master จะส่งหมายเลข arbitrationไปยังสายสัญญาณร่วมที่เรียกว่า shared-bus request/grant(SBRG) ซึ่งจะอยู่บน arbitration bus ตัวเลขถูกส่งผ่านตัวarbiterของตัวเอง จากนั้น arbiter ของแต่ละ master จะทำการเปรียบเทียบค่าของหมายเลขarbitration ของตัวเองกับหมายเลข arbitration ที่อยู่บนสายสัญญาณ SBRG หากหมายเลขที่อยู่บน SBRGมากกว่า request นั้นจะถูกปล่อยไป แต่หากหมายเลขบน arbiterมากกว่า หมายเลขบน SBRG จะเปลี่ยนเป็นหมายเลขนั้น และ master ที่เป็นเจ้าของหมายเลขจะเป็นผู้ใช้บัสรายถัดไป

เห็นได้ชัดว่าการทำงานแบบ Distribute Arbitration เป็นแบบ priority-based วิธีการแบบนี้พบได้บนระบบbus Multibus II และ Futurebus+ นอกจากวิธีการdistributed arbitrationแล้ว ระบบ Futurebus+ ยังสามารถเลือกใช้วิธีการแบบ separate central arbiterได้อีกด้วย

Transaction Mode

การส่งสัญญาณแบบ address-only transfer ประกอบไปด้วยการส่งรายละเอียด address อย่างเดียวโดยที่ไม่มีการส่งข้อมูลใดๆตาม สำหรับการส่งสัญญาณแบบ compelled data transfer จะประกอบไปด้วยการส่งรายละเอียด address ไปก่อน จากนั้นจะเป็นการส่งกลุ่มข้อมูล(data block)จำนวน 1 กลุ่มหรือมากกว่าไปยัง 1 addressหรือมากกว่า 1 addressที่อยู่ติดกัน ส่วนการส่งสัญญาณแบบ packet data transfer ประกอบไปด้วยการส่งรายละเอียด address ตามด้วยการส่งรายละเอียดข้อมูลที่มีความยาวคงที่ค่าหนึ่งซึ่งเรียกว่า data packet โดยที่ packet เหล่านี้จะถูกส่งไปยังกลุ่มของ address ที่อยู่ติดกัน

การทำงานหลักๆที่พบนระบบบัสคือการจัดการเกี่ยวกับ data transfer และ interruption ส่วน bus-transaction หลักๆ จะประกอบด้วยสัญญาณ request และสัญญาณ respond ประเภทของ transaction แยกได้ดังนี้

- Connected transaction: จะนำส่งข้อมูลทั้งrequestของmaster และrespondของslaveใน bus transaction เดียว

- Split transaction: จะแยกส่วนของ request และ respond ออกเป็นคนละ bus transaction การส่ง transaction แบบนี้จะยอมให้อุปกรณ์สามารถเรียกใช้บัสได้นาน และสามารถใช้ทรัพยากรของบัสในแบบที่มีประสิทธิผลกว่า นอกจากนั้นสามารถใช้ split transaction ระหว่างบัสหลายๆตัวเพื่อใช้สำหรับการจัดการการใช้งาน cahce บนระบบ multiprocessor ขนาดใหญ่ สำหรับ trsansaction ที่เป็นแบบ complete split transaction อาจประกอบไปด้วย connected bus transaction 2 transaction หรือมากกว่านั้น

Interrupt Mechanism

Interrupt เป็น request ที่ถูกส่งมาจาก I/O หรืออุปกรณ์ใดๆที่ต้องการเรียกใช้บริการ (service) สัญญาณ interrupt จะถูกส่งผ่านทาง priority interrupt signal โดยมี functional module ตัวหนึ่งที่ทำหน้าที่คอยจัดการเกี่ยวกับสถานะและIDของ interrupt Priority interrupts สามารถถูกจัดการได้หลายรูปแบบ เช่น

- VME bus ใช้สายสัญญาณ interrupt-request 7เส้น interrupt ที่เกิดขึ้นจะถูกจัดการโดยสายสัญญาณทั้ง 7 เส้นนี้

- การจัดการโดยการส่งข้อความ(message)บน data bus line โดยอยู่บนหลักการของ time-sharing วิธีการนี้จะไม่ใช้สายสัญญาณ interrupt แต่ต้องใช้ bus cycle มากขึ้นในการจัดการ interrupt message ที่ส่งมา การจัดการ interrupt โดยไม่ใช้สายสัญญาณ interrupt เรียกว่า ‘virtual interrupt’ ในระบบ Futurebus+ ไม่มีการใช้สายสัญญาณ interrupt เพราะระบบนี้สามารถควบคุม interrupt ที่เกิดขึ้นได้ดีโดยการใช้ virtual interrupt บน data bus

IEEE Futurebus+ Standards

มาตรฐานการผลิต Backplane bus ในปัจจุบันมีอยู่มากมายตามบริษัทที่ทำการผลิต ตัวอย่างของระบบบัสที่เป็นที่รู้จักกันคือ VME, Multibus II, Nubus, Fastbus, Nanobus โดยบริษัท Encoore Computer System

บางส่วนของบัสเหล่านี้ถูกนำไปใช้ในการผลิต Multi-processor อย่างไรก็ตาม bus แต่ละแบบก็มีข้อจำกัดแตกต่างกันไป และส่วนมากจะรองรับการทำงานการส่งข้อมูลที่ 32-bit แต่ยังไม่มีระบบบัสใดที่สามารถจัดการเรื่องของการใช้งานcacheอย่างมีประสิทธิภาพ หรือการจัดการในเรื่องการ inter-processor synchronization

มาตรฐาน Futurebus+ ได้รับการพัฒนา โดยความร่วมมือระหว่าง VME International Trade Association, Multibus Manufacturing Group, U.S Navy Next Generation Computer Resources Program, IEEE, และผู้เชี่ยวชาญจากบริษัทและมหาวิทยาลัยต่างๆ

วัตถุประสงค์ในการพัฒนาบัสระบบใหม่ เพื่อให้เป็นระบบเปิดที่สามารถรองรับการทำงานที่ 64-bit address และก่อให้เกิดผลลัพธ์ที่สามารถทำงานได้กับระบบ multi-RISC (Reduce Instruction Set Computer) หรือเพื่อเป็นแม่แบบสำหรับสถาปัตยกรรมแบบ multiprocessor ในอนาคต

มาตรฐานบัสแบบใหม่นี้ต้องสามารถทำการปรับเปลี่ยนขนาดการทำงานได้ (Scalable) และต้องไม่ขึ้นกับสถาปัตยกรรมหรือเทคโนโลยีอันใดอันหนึ่งโดยเฉพาะ ความสามารถการทำงานหลักๆของระบบ Futurebus+มีดังนี้

Standard Requirement

วัตถุประสงค์หลักของ Futurebus+ คือ เพื่อเป็นการสร้างมาตรฐานที่จะนำไปสู่ก้าวต่อไปในการพัฒนาความสามารถการทำงานของระบบ multiprocessor ในอนาคต สิ่งนี้เป็นการปูพื้นฐานสำหรับระบบคอมพิวเตอร์ ข้อสรุปต่อไปนี้เป็นความต้องการทางการออกแบบที่จัดทำขึ้นโดย IEEE

- เป็นระบบที่ไม่ขึ้นกับสถาปัตยกรรม ,โปรเซสเซอร์ และเทคโนโลยี และต้องเป็นระบบเปิดสำหรับนักออกแบบทุกคน

- ใช้วิธีการ asynchronous timing protocol ในการจัดการการส่งข้อมูล พร้อมกับระบบการควบคุมการส่งข้อมูลแบบ handshaking

- สามารถเลือกการทำงานแบบ source-synchronize protocol สำหรับการส่ง data block ความเร็วสูง

- มีความสามารถในการทำ parallel arbitration เพื่อรองรับการทำงานที่มี bus-transaction หลายแบบ รวมทั้งการส่ง transaction ที่เป็น Broadcall, broadcast และ three-party transaction

- ระบบมีความเที่ยงตรง และสามารถรองรับการทำงานที่ผิดปกติของ application พร้อมกันนั้นสามารถรองรับการเสียบหรือถอด card ที่ยังทำงานอยู่ (live card)ได้ ,มี parity check สำหรับทุกสายสัญญาณ , มี feedback checking และการปรับตั้งค่าระบบแบบ dynamic (dynamic system reconfiguration)ในกรณีที่ระบบล่มต้องไม่เป็นในรูปแบบของการส่งผ่านสัญญาณแบบ daisy-chain

- มีกลไกในการป้องกัน dead-lock หรือ live-lock

- เป็นการทำงานแบบการปรับโดยใช้วงจร (circuit switch) และ split transaction พร้อมกับรองรับการชุดคำสั่งสำหรับหน่วยความจำ(memory command) เพื่อใช้ในการทำ remote locking และการทำงานที่คล้ายแบบ SIMD (Single Instruction Multiple Data stream)

- รองรับการคำนวณ mission-critical ในแบบทันทีทันใด (real-time) พร้อมกับมีการจัดการในเรื่องของ priority และต้องรองรับการทำงานแบบ distributed clock synchronization

- รองรับการทำงานแบบ 32-bit หรือ 64-bit address และส่งข้อมูลที่ 32 – 64,128,256 bitเพื่อให้สามารถทำงานที่ bandwidth ต่างๆกันได้

- สามารถทำงานทำงานแบบ snoopy cache-based multiprocessor เพื่อรองรับระบบขนาดใหญ่ที่มีการเชื่อมต่อระบบบัสหลายๆตัวได้

- สามารถใช้งาน message-passing กับการเชื่อมต่อแบบ multicomputer ได้

ตัวอย่างสายสัญญาณบนมาตรฐาน Futurebus+

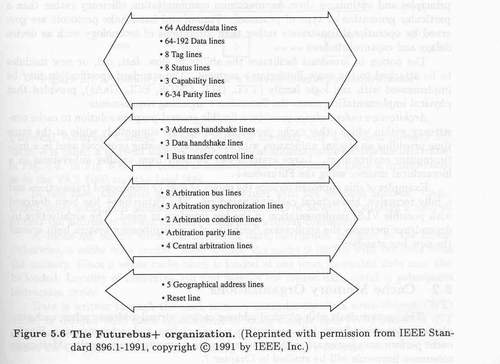

จากภาพที่ 5.6 ระบบ Futurebus+ ประกอบด้วยส่วน information, synchronization, arbitration และสายสัญญาณ handshake ที่สามารถทำงานได้กับระบบที่มีการออกแบบที่แตกต่างกัน มาตรฐานนี้มี 64-bit address, และสามารถทำงานแบบ multiplex กับสายข้อมูลแบบ 64-192 bit data ทำให้สามารถส่งข้อมูลได้ถึง 256 bit ส่วนสาย tag-line เอาไว้ใช้สำหรับการเลือกโหมดการทำงานของการส่ง address/data

Command-line ใช้สำหรับการส่งรายละเอียดคำสั่งจาก masterไปยัง slave หนึ่งตัวหรือมากกว่า สาย status-line ถูกใช้งานโดย slave เพื่อทำการส่งข้อมูลตอบกลับไปยัง master ส่วน capability-line ใช้ในการระบุ bus-transaction แบบพิเศษ โดยที่ทุกๆ byte ของสายสัญญาณจะต้องมีสาย parity-check

สัญญาณ Synchronization ถูกใช้เพื่อช่วยในการกำหนดจังหวะของการแลกเปลี่ยน address, command, capability status และ data สำหรับ address handshake-line และ data-handshake-line จะถูกใช้งานโดย master และ slave ส่วน tenure-lineจะถูกใช้ในการส่งคำสั่งควบคุมบัส (bus control)

Arbitration-bus-line ใช้ในการเก็บหมายเลข arbiter สำหรับกระบวนการเลือกตัดสินโพรเซสเซอร์ ส่วนเส้นสัญญาณ synchronization และ condition ใช้สำหรับการทำ handshaking และการกำหนดเงื่อนพิเศษตามลำดับ

Central arbitration-line ถูกใช้ในกรณีระบบมีการใช้งาน central bus control ส่วน miscellaneous-line ถูกใช้สำหรับการกำหนดหมายเลขของ geographical address หรือ slot address และยังถูกใช้สำหรับการ initial ระบบในกรณีที่มีการ reset หรือหลังจากการเสียบcard

จำนวนสายสัญญาณทั้งหมดอยู่ในช่วง 91,127,199,343 สำหรับ 32, 64,128,256-bit ตามลำดับ นอกจากนั้นอาจต้องมีสายสัญญาณอื่นเพิ่มเพื่อใช้สำหรับงาน utility เช่น สัญญาณนาฬิกา, แหล่งพลังงาน

Technology/Architecture Independence

มาตรฐาน Futurebus+ เป็นมาตรฐานที่ไม่ขึ้นกับเทคโนโลยีและสถาปัตยกรรมที่ใช้ โดยการทำงานจะอยู่บนพื้นฐานของหลักการพื้นฐานทั่วไป และมุ่งหวังให้สามารถสื่อสารระหว่างกันให้ได้มากที่สุด แทนที่จะถูกจำกัดไว้ด้วยรุ่นของระบบหรือชนิดของโพรเซสเซอร์ สำหรับหลักการ Timing และ handshaking ได้รับการจัดสร้างมาจากเงื่อนของการทำงาน แทนที่จะเป็นเป็นข้อจำกัดทางด้านเทคโนโลยี เช่นความล่าช้าของอุปกรณ์ และ capture windows

ด้วยรูปแบบการทำงานที่เป็นแบบ Broadcast ทำให้อุปกรณ์ที่ช้า, เร็ว, เก่า และใหม่สามารถทำงานร่วมกันได้บน Futurebus+ เดียวกัน อีกทั้งมาตรฐานนี้สามารถสร้างจากอุปกรณ์ทางด้านตรรกะแบบ (logic semiconductor) ใดๆ ก็ได้ เช่น TTL (Transistor Transistor Logic), BTL (Backplane Transceiver Logic), CMOS (complementary metal oxide semiconductor), ECL (Emitter Couple Logic), GaAs (Gallium Arsenide)

การไม่ขึ้นกับสถาปัตยกรรมทำให้สามารถทำงานร่วมกับ Cache ที่มี protocol แบบอื่นได้ และในขณะเดียวกัน สามารถทำงานเป็นอันหนึ่งอันเดียวกันในการส่ง message ในสภาวะแวดล้อมที่เป็น multi-computer อีกทั้งระบบคอมพิวเตอร์ใหญ่ๆสามารถสร้างขึ้นได้จากระบบย่อยหลายๆอัน ในลักษณะการเชื่อมแบบลำดับขั้น (hierarchical) โดยใช้ Futurebus+

จากตัวอย่างแนวคิดนี้ได้รวมทางเลือกเกี่ยวกับ Split/interlocked transaction, การทำงานแบบ Recursive แบบเต็มรูปแบบ และการจัดการ cacheแบบลำดับขั้น (Hierarchical Cache Paradigm) Futurebus+ ได้รับการออกแบบให้มี bus interfaceที่เป็น VLSI (Very Large Scale Integration) สิ่งเหล่านี้จะช่วยให้เกิดความยืดหยุ่นสำหรับระบบ multiprocessor ที่ล้อมรอบไปด้วยมาตรฐานระบบบัสแบบใหม่ๆ

ตอนที่ 1 / ตอนที่ 2 / ตอนที่ 3

ผู้เขียน/อ้างอิง : จักรกฤษณ์ แร่ทอง

อื่น ๆ เกี่ยวกับไอ.ที.

เมกะไบท์ กิกะไบท์ เทราไบท์ แล้วต่อไปจะเป็นอะไร ?

Trend of technology จะพูดถึง แนวทางของ Bus ในอนาคต

Trend of technology จะพูดถึง แนวทางของ Bus ในอนาคต

ครื่องวัดความดัน วัดอุณหภูมิ และตรวจนับการเต้นของชีพจร

คิดว่าหลายท่านที่ติดตามข่าวสารผ่านสื่อต่างๆ ในช่วงปีกว่ามานี้ คงจะได้ยินคำว่าสภาวะโลกร้อนหรือ Global Warming

จะเลือกจอ CRT หรือ LCD ดี? คำถามนี้อาจเป็นคำถามที่หลายๆคนถามหา เมื่อจะเลือกซื้อจอใหม่

การใช้งานเลขรหัสสินค้าอิเล็กทรอนิกส์ ร่วมกับเทคโนโลยี RFID (Radio Frequency Identification) มีประสิทธิภาพสูง

ระบบเสมือนจริงนับเป็นการใช้ประโยชน์จากการแสดงผลด้วยสื่อประสม สร้างภาพ 3 มิติที่สามารถมองเห็นเหมือนเป็นภาพที่เป็น 3 มิติ

เอาดิสก์หลายๆตัวมารวมกัน ประสิทธิภาพที่ได้จากการใช้งานจะมากกว่า

เทคโนโลยีสื่อสารไร้สาย แต่ในอนาคตอันใกล้นี้

ความคิดเห็น/แนะนำ/ติชม/อื่นๆ

- คนตัวใหญ่ [25 ส.ค. 2551 , 09:39 AM]

ดีมากค่ะ ให้ความรู้ได้หลากหลายดีค่ะ

- ปนัดดา [19 ก.ย. 2553 , 10:13 AM]

ผมก็อปปี้ไม่ได้ครับ

- สุจิตรา [08 ต.ค. 2555 , 06:07 PM]

ข้อมูลเป็นประโยชน์มากค่ะ ตอนนี้กำลังทำรายงานหัวข้อนี้อยุ่พอดี ขอบคุณมากๆค่ะ